FPGA入門:數(shù)碼管靜態(tài)顯示原理與實現(xiàn)

一、 數(shù)碼管簡介

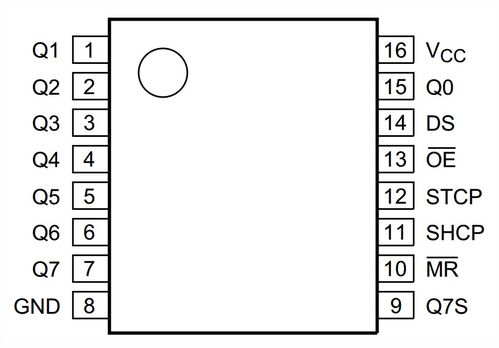

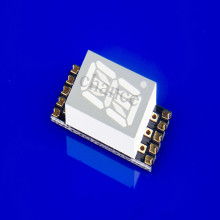

數(shù)碼管是一種常見的顯示器件,廣泛應(yīng)用于數(shù)字時鐘、儀器儀表等設(shè)備中。它由多個發(fā)光二極管(LED)組成,通過點亮特定的LED段來顯示數(shù)字(0-9)或部分字母(A-F)。最常見的類型是七段數(shù)碼管,其包含a、b、c、d、e、f、g七個發(fā)光段以及一個小數(shù)點dp段,共8個控制引腳。

二、 靜態(tài)顯示原理

靜態(tài)顯示是指每個數(shù)碼管的每一個段碼都由一個獨立的I/O端口(或譯碼器輸出)進行驅(qū)動。當一個數(shù)碼管需要穩(wěn)定地顯示一個數(shù)字時,F(xiàn)PGA需要持續(xù)地向其對應(yīng)的段碼引腳輸出固定的高電平或低電平(取決于數(shù)碼管是共陽極還是共陰極),以維持其點亮狀態(tài),直到需要改變顯示內(nèi)容為止。

對于單個數(shù)碼管,靜態(tài)顯示的實現(xiàn)非常簡單直接,無需復(fù)雜的動態(tài)掃描邏輯。其核心步驟是:

- 確定數(shù)碼管類型:共陽極數(shù)碼管的公共端接高電平,段碼端輸入低電平來點亮對應(yīng)的段;共陰極數(shù)碼管的公共端接低電平,段碼端輸入高電平來點亮。

- 創(chuàng)建段碼表(真值表):根據(jù)要顯示的數(shù)字(0-9),確定需要點亮的段(a-g, dp),并將其編碼成FPGA I/O口能夠輸出的二進制值。例如,對于一個共陰極數(shù)碼管,要顯示數(shù)字“0”,則需要點亮a, b, c, d, e, f段(g段和dp段熄滅),對應(yīng)的8位二進制碼可能是

8'b0011_1111(假設(shè)a段對應(yīng)最低位)。 - FPGA引腳分配與編碼:在FPGA開發(fā)環(huán)境中,將設(shè)計好的段碼輸出信號分配到實際的硬件引腳上,這些引腳通過限流電阻連接到數(shù)碼管的段碼引腳。

三、 FPGA實現(xiàn)步驟(以Verilog HDL為例)

假設(shè)我們的目標是在一個共陰極數(shù)碼管上靜態(tài)顯示數(shù)字“5”。

1. 模塊定義:

`verilog

module seg_static(

input wire clk, // 系統(tǒng)時鐘(雖然靜態(tài)顯示不一定需要時鐘,但通常引入以便于擴展)

output reg [7:0] seg // 數(shù)碼管段碼輸出,[7:0]分別對應(yīng) dp, g, f, e, d, c, b, a

);

`

2. 段碼編碼:

我們需要一個查找表(LUT),將數(shù)字值映射到對應(yīng)的段碼。這里我們直接輸出固定數(shù)字“5”的編碼。對于共陰極數(shù)碼管,顯示“5”需要點亮a, f, g, c, d段。假設(shè)我們的位序是 seg[0]=a, seg[1]=b, ..., seg[6]=g, seg[7]=dp,那么“5”的段碼為 8'b0110_1101(其中1表示點亮,0表示熄滅)。

3. 邏輯實現(xiàn):

`verilog

// 將數(shù)字“5”的段碼常量賦值給輸出端口

always @(posedge clk) begin

seg <= 8'b01101101; // 這是數(shù)字5的段碼,具體編碼需根據(jù)硬件連接順序調(diào)整

end

`

實際上,對于純粹的靜態(tài)顯示,甚至可以不使用時鐘,直接使用連續(xù)賦值語句:assign seg = 8'b0110</em>1101;。使用時鐘觸發(fā)器(always @(posedge clk))是為了代碼風(fēng)格的一致性和未來擴展為動態(tài)顯示或顯示內(nèi)容可變時更容易修改。

4. 引腳約束:

在FPGA廠商的約束文件(如Xilinx的XDC文件或Intel的QSF文件)中,將 seg[7:0] 信號映射到實際連接數(shù)碼管段的FPGA引腳上。

四、 擴展與注意事項

- 多位數(shù)碼管靜態(tài)顯示:如果系統(tǒng)中有多個數(shù)碼管需要顯示不同內(nèi)容,采用靜態(tài)顯示意味著每個數(shù)碼管的每個段都需要一個獨立的I/O引腳,這會導(dǎo)致I/O資源消耗巨大。例如,4個8段數(shù)碼管需要4*8=32個I/O。因此,靜態(tài)顯示通常只用于單個或極少數(shù)碼管的場合。

- 限流電阻:為了防止過電流損壞LED段,必須在FPGA引腳和數(shù)碼管段碼引腳之間串聯(lián)限流電阻(通常為100Ω至1kΩ)。

- 亮度與功耗:靜態(tài)顯示時,點亮的LED段持續(xù)導(dǎo)通,亮度穩(wěn)定,但相比動態(tài)掃描方式,其功耗可能更高(尤其是多位數(shù)碼管時)。

- 從靜態(tài)到動態(tài):當需要驅(qū)動多位數(shù)碼管時,更常用的方法是動態(tài)掃描顯示。它利用人眼的視覺暫留效應(yīng),通過快速輪流點亮各個數(shù)碼管,并同步改變段碼數(shù)據(jù),從而用較少的I/O引腳(n個公共端+8個段碼端)實現(xiàn)n位數(shù)碼管的顯示。靜態(tài)顯示是理解這一更復(fù)雜技術(shù)的重要基礎(chǔ)。

五、

數(shù)碼管靜態(tài)顯示是FPGA入門學(xué)習(xí)中的一個經(jīng)典實踐項目。它幫助初學(xué)者理解數(shù)字系統(tǒng)的基本輸出控制、二進制編碼、硬件描述語言對硬件行為的建模,以及FPGA引腳分配的全流程。通過成功點亮一個數(shù)碼管并顯示指定數(shù)字,可以建立起操作FPGA外部設(shè)備的信心,為后續(xù)學(xué)習(xí)更復(fù)雜的接口和時序邏輯設(shè)計打下堅實基礎(chǔ)。

動手建議:在完成單個數(shù)碼管靜態(tài)顯示后,可以嘗試修改代碼,通過撥碼開關(guān)或按鍵輸入來改變顯示的數(shù)字,實現(xiàn)一個簡單的可控顯示,這將涉及組合邏輯和輸入接口的學(xué)習(xí)。